[10000印刷√] 8对1多工器真值表 663528-8对1多工器真值表

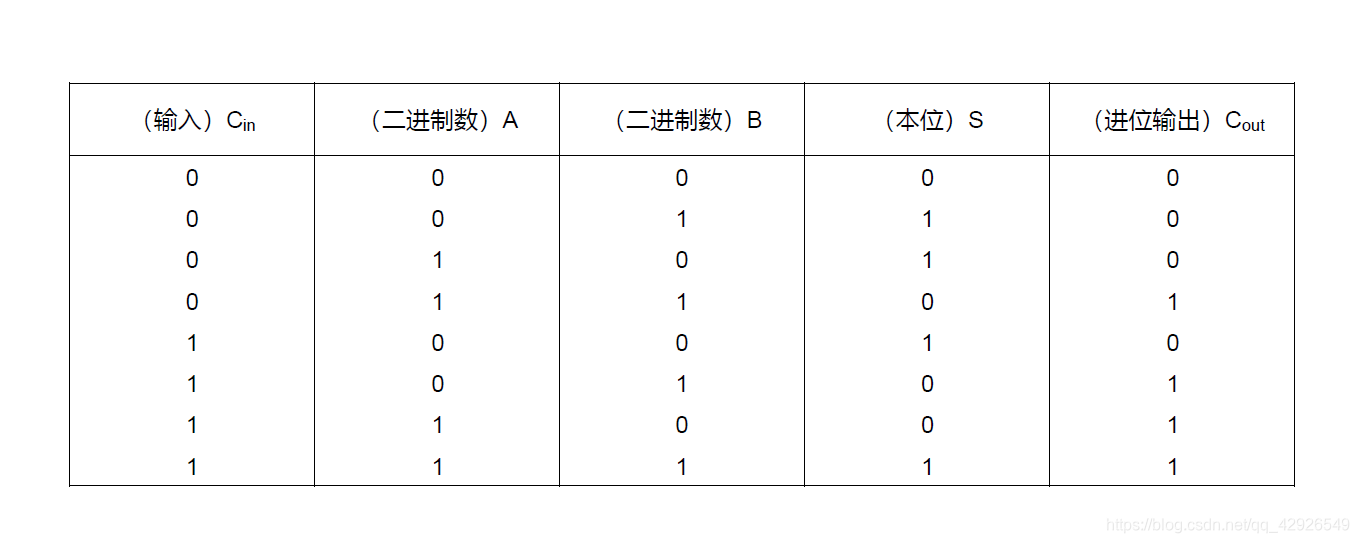

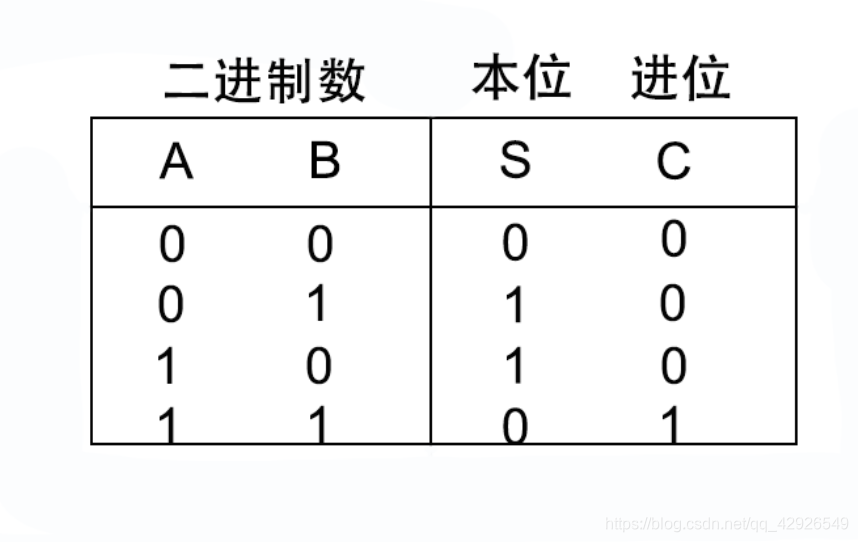

编码器 复习 ?1半加器和全加器的概念及特点? ?2集成全加器74ls2的逻辑功能及应用? ?3集成数值比较器的逻辑功能及应用? 1 33 编码器和译码器 ?331 编 工人们常说的8公斤的压力是指多少MPa的压力? 1Pa大小:一张平铺的报纸对水平桌面的压强,3粒芝麻对水平桌面的压强为1Pa。 我就奇了怪了,连受压面积是多少都不知道,就能知道压强的多大的答案都能被采纳? 一位加法器的真值表见表11;由表中可以看见,这种加法没有考虑低位来的进位,所以称为半加。 半加器 就是实现表11中逻辑关系的电路。 被加数A加数B和数S 进位 C 表11一位半 加法器 真值表 半加器 和 全加器 的原理及区别(结构和功能) 全加器

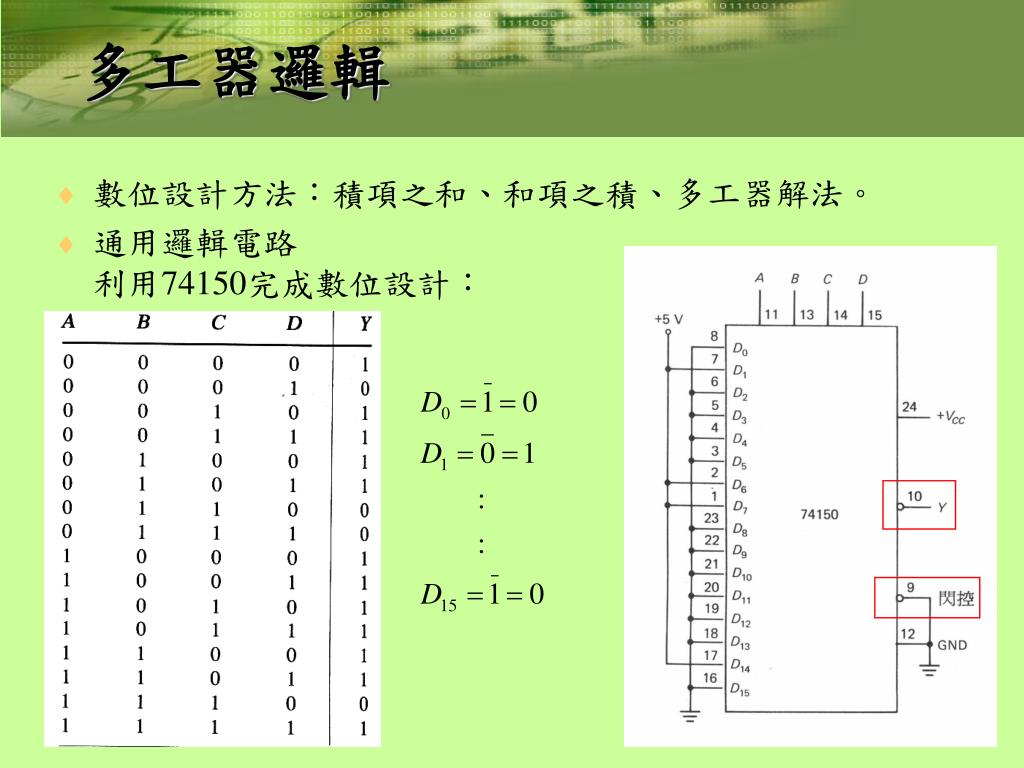

100學年度第2學期邏輯設計實習ta訓練基本介紹 Ppt Download

8对1多工器真值表

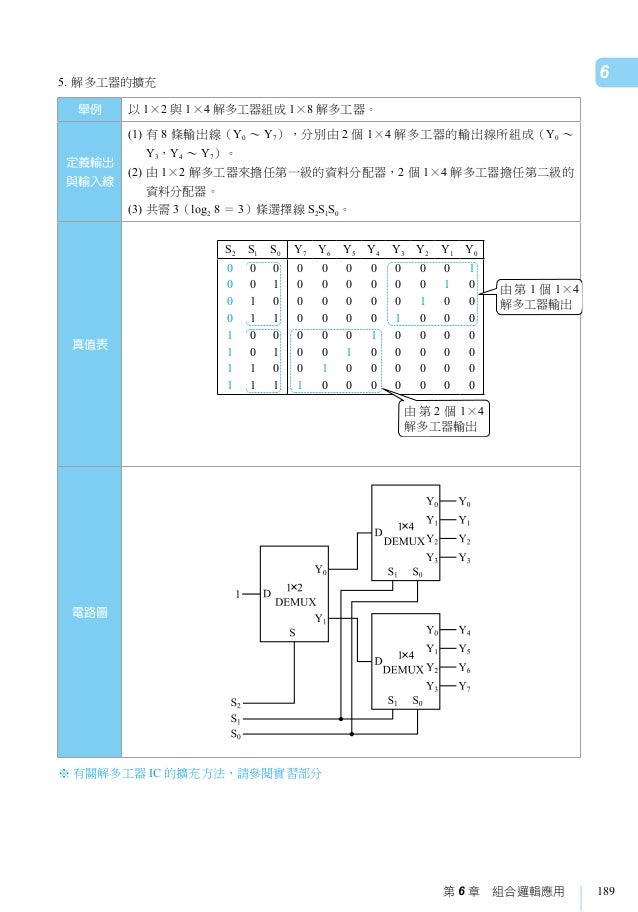

8对1多工器真值表- 真值表如下: 2、方案实施 (1)设计思路 四选一多路选择器设计时,定义输入s为标准以内漏记为sidlogic输出的信号z的数据类型定义为2位标准逻辑矢量位std_logic_vector(1downto0)。使用lbraty语句和use语句,来打开ieee库的程序包stdlogic_1164all。 cd4042b真值表 cd4532b: cmos的8位优先级编码器,用于对cd4042b锁存的数据进行编码。 cd4532b实物图 cd4532b引脚定义 cd4532b真值表 测试 时钟发生器部分

Ppt 邏輯電路的分類powerpoint Presentation Free Download Id

1 @Table(name="t_double_one2many_order") 2 @Entity 3 public class Order2 { 4 5 private Integer id;4位全加器设计解析 可编程逻辑器 件设计大作业 题 学 班 姓 学 目 院 级 名 号 四位全加器设计 自动化与电气工程学院 2104 年 12 月 30 日 目录 摘要 一般常见的管排数28排 当然特殊情况下也有更大的。给出一个经验值 :表冷器迎面风速25m/s 铜管管径158 翅片间距25mm 翅片高度4mm 管排数8排的表冷器 湿工况下 阻力为400Pa左右 希望对你的问题有所帮助。

38译码器真值表讲解从这个名字来剖析,三八译码器,就是把 3 种输出形态翻译成 8 种输入形态。从图 315所能看出来的,74hc138 有 1~6 一共是 6 个输出引脚,然则个中 4、5、6 这三个引脚是使能引脚。使能引脚和我们前边讲 74hc245 的 oe 引脚是一样的7 8 //n的一方有对1的一方的对象的引用 9 //①要有映射注解表明为映射;②、允许多对一,否则就是一对一 10 private Customer2 customer; 先给大家看一下我的项目 整个的一个 构造: 好,然后 开始我的 mybatis 关系,用的是mysql 1首先,先导入依赖: dependency> groupId>junitgroupId> artifactId>junitartifactId> version>412version> scope>testscope> dependency> mybatis 的一对多, 多对一 ,以及多对对的 配置 和使用 JavaAlliance

哈尔滨工业大学华德应用技术学院课程设计用纸 功能及方框图21 功能简介 彩灯控制器能够使彩灯控照一定的形式和规律闪亮,起到烘 托节日氛围、吸引公众注意力的作用。 彩灯控制器多种多样,本 设计的彩灯控制器主要功能 (1)可以控制8 路彩灯。 (2 大 嘴 棋 牌 破 解电脑版从数据上看,北京、上海等大城市的三甲医院,住院人次占全市住院人次的比例,由过去的50%左右涨 集成三线—八线译码器除了3线到8线的基本译码输入输出端外,为便于扩展成更多位的译码电路和实现数据分配功能,还有三个输入使能端 en1, en2a和en2b 。真值表和内部逻辑图分别见表1和图1(a)。

Untitled Document

數位邏輯學 第八章

CNC CNBA CNA CNC CN C CN C CN C CN B A CNB A CN BA CN A CN A CN A CN C CN C CN C Authority CN China Prior art keywords input type flip flip3 数字式工频有效值多用表4(第四届,1999年) (1)设计任务题目 设计并制作一个能同时对一路工频交流电(频率波动范围为50±1Hz、有失真的正弦波)的电压有效值、电流有效值、有功功率、无功功率、功率因数进行测量的数字式多用表。参见图1324。 2算术平均值原理 (1)算术平均值的意义 当测量次数足够多时则近似认为,随机误差的数学期望等于0。即在仅有随机误差的情况下,当测量次数足够多时,测量值的平均值接近于真值。 则第i次测量得到的测得值xi与真值之间的绝对误差就等于随机误差,

邏輯電路的分類1 組合邏輯 Combinational Logic 其輸出狀態直接由輸入的組合來決定 並不涉及線路過去的輸出狀態 Ppt Download

Untitled Document

二选一数据选择器介绍doc,二选一数据选择器 目录 一:数据选择器的基本原理 3 二 电路逻辑功能 3 21 电路逻辑图 3 22真值表与表达式 3 23电路设计及仿真 4 三 版图设计 6 31总体版图设计及DRC验证 6 311数据选择器版图设计步骤 6 312版图验证 9 32版图仿真 10 四 数据选择器版图LVS对比 11 五 结论及 真值 : 符号位 X 一般 0 正 1负 负数: 8 二进制8位表示 : 1)真值 X : 1000 2)原码:1 3)反码:1 (符号位不变,其余位 取反 ) 4)补码:1 (符号位不变,最后一位 加一 ) 0 补 = 0 补 = 5)偏置值: 题目 给出 (eg1字长为8位,偏置值为 2∧7 eg2 iee 754 段浮点8对1多工器 真值表 (11)进行仿真并出波形,观看波形图,对照真值表,检查结果正确与否 根据电路图并使用 LEdit 设计出数据选择器的版图如下所示 图 31 总体版图设计 312 版图验证 设计好后进行版图 DRC(设计规则)检查,没有错误,如下图所示 8 集成电路 CAD 课程设计 图 32

Http My Stust Edu Tw Sys Read Attach Php Id 5849

Ppt 邏輯電路的分類powerpoint Presentation Free Download Id

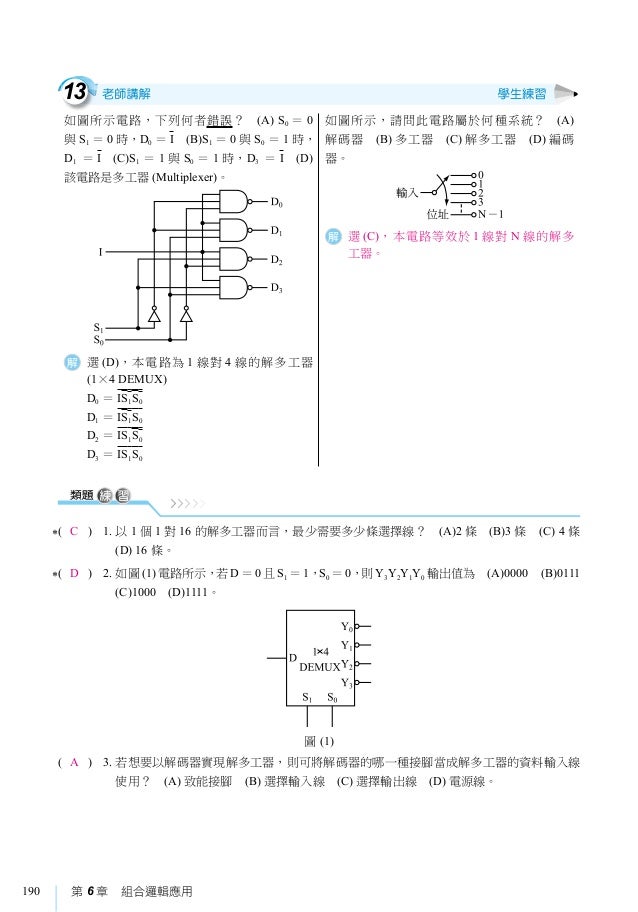

(2) 对定时抢答功能的处理 实验初期,对十进制加减法计数器 74ls192 的真值表和 555 定时器各功能端度没 能掌握,导致对置数和产生脉冲进行减数两个功能都没能实现,后经过上网和到图书 馆查阅资料,并在老师的解释下,了解了如何正确使用,经多次连接 cc4512功能表 dis inh a2 a1 a0 y 0 0 0 0 0 d0 0 0 0 0 1 d1 0 0 0 1 0 d2 0 0 0 1 1 d3 0 0 1 0 0 d4 0 0 1 0 1 d5 0 0 1 1 0 d6 0 0 1 1 1 d7 0 1 × × × 0 1 × × × × 高阻 解:逻辑函数: 电路连接图为: 4、555定时器构成单稳态触发器如图(a)b)。11 12 // 省略getter、setter方法 13}

掌握 數位邏輯 含實習 複習講義電子試閱本

Ppt 邏輯電路的分類powerpoint Presentation Free Download Id

表1 为样品电容器校准中常用基准液体室温下介电常数值。假设已知液体为乙醇(c2h6o),其室温环境下可由表1 得介电常数真值为243,则c0 真值就可以通过公式(17)得到,随后可以通过公式(18)得到就样品电容器的附加电容c 附加。 表1 常用基准液介电常数值True table; 网络释义: True Table; 图31 优先编码器功能仿真图 对其仿真图进行仿真分析:din 为输入信号组,它由din7din0 八个输入信 号组成。output 为输出信号组, 它由output2output0 三个二进制代码输出信 号组成。enable 时编码器工作,当使能端为1时输出 高阻状态。

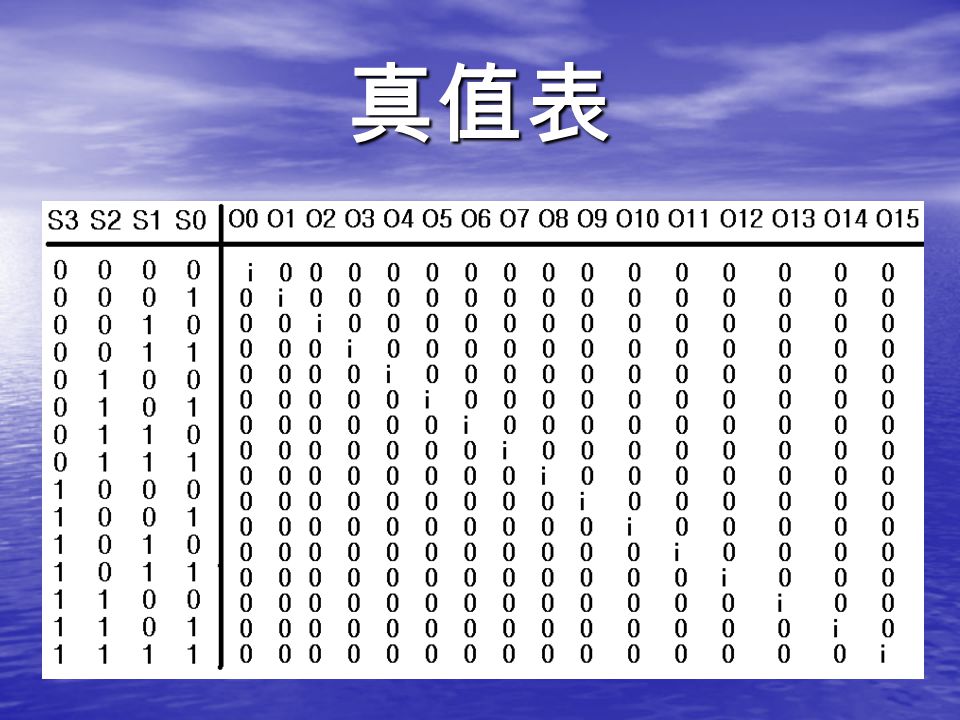

Vhdl 邏輯設計題目 一對十六解多工器題目 一對十六解多工器姓名 李國豪姓名 李國豪學號 b09322001 學號 b09322001 Ppt Download

Cd74hc4067 16 對1 或1 對16 通道 類比 數位 多工器 解多工器 模組 露天拍賣

数字电路与逻辑设计 通过上面对图623和图624的分析,可得 出555各功能端的真值表,如下表621所示。 由表621可看出,s、r、mr的输入不一 定是逻辑电平,可以是模拟电平,因此,该集成 电路兼有模拟和数字电路的特色。6 private String orderName; mybatis 详解(七)一对一、一对多、多对多 目录 1、一对一 2、一对多 3、多对多 前面几篇博客我们用mybatis能对单表进行增删改查操作了,也能用动态SQL书写比较复杂的sql语句。 但是在实际开发中,我们做项目不可能只是单表操作,往往会涉及到多张表

Http My Stust Edu Tw Sys Read Attach Php Id 5849

Ppt 第四章powerpoint Presentation Free Download Id

基于 OLAP 源数据的计算 对于创建自 OLAP 多维数据集的数据透视表,会在 OLAP 服务器上预先计算汇总值,然后在 Excel 中显示结果。 不能更改这些预计算值在数据透视表 中的计算方式。 例如,不能更改用于计算数据字段或分类汇总的汇总函数,也不能添加计算 数电试题与答案(五套)doc,PAGE PAGE 1 《数字电子技术基础》试题一 填空题(22分 每空2分) 1、 , 。 2、JK触发器的特性方程为: 。 3、单稳态触发器中,两个状态一个为 态,另一个为 态多谐振荡器两个状态都为 态, 施密特触发器两个状态都为 态 4、组合逻辑电路的输出仅仅只与该时刻的 有关,而与修订日志: 第3题答案由b改为d。 第29题搞明白是什么了,但答案很奇怪,为0,与选项不符。 第17和双选4还是不会。单选部分1、cisc的全称是什么( )。da 精简指令系统计算机 b 复杂指令系统控制器c 精简指令系统控制器 d 复杂指令系统计算机 复杂指令集计算机(cisc),risc(精简

Http My Stust Edu Tw Sys Read Attach Php Id 5849

掌握 數位邏輯 含實習 複習講義電子試閱本

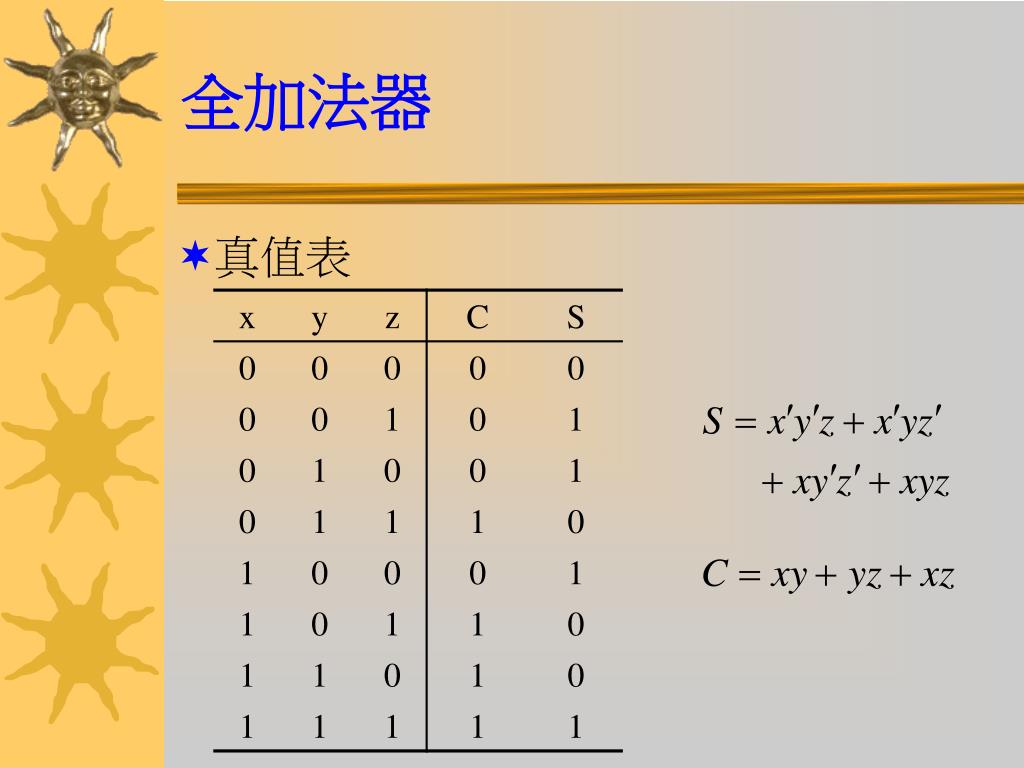

必应词典为您提供真值表的释义,拼音zhēn zhí biǎo,n truth table;Iso rms系列 真有效值(rms)信号隔离放大器模块是以单片trms/dc 转换器为核心并采用了全新的ds计算技术,配置高精度信号隔离放大器构成使用这种模块能准确、实时测量各种信号波形的有效值,无须考虑波形参数和失真真有效值真有效值测量真有效值信号真有效值转换真有效值放大器 十六位全加器的基本原理: 16 位全加器设计的基本思想,就是仿照通常的解组合逻辑电路的方法,先把原理图画出来, 然后通过原理图把各个信号量描述出来,最后再根据各个器件的逻辑功能列出真值表。 当全 加器工作时,先一个一个二进制数全部按位输入

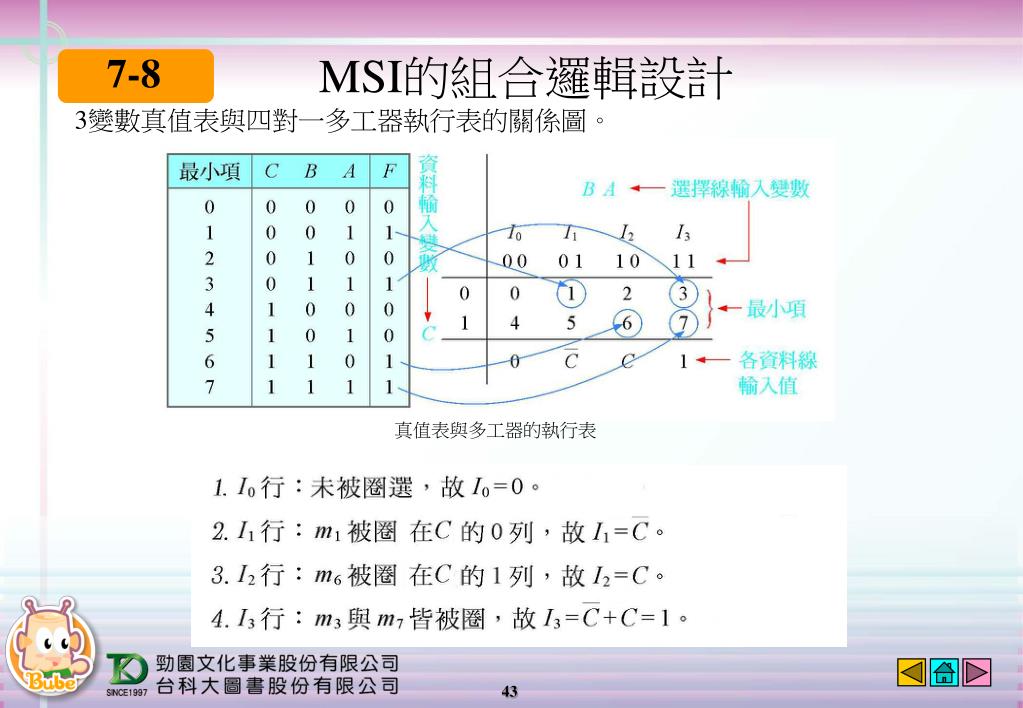

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

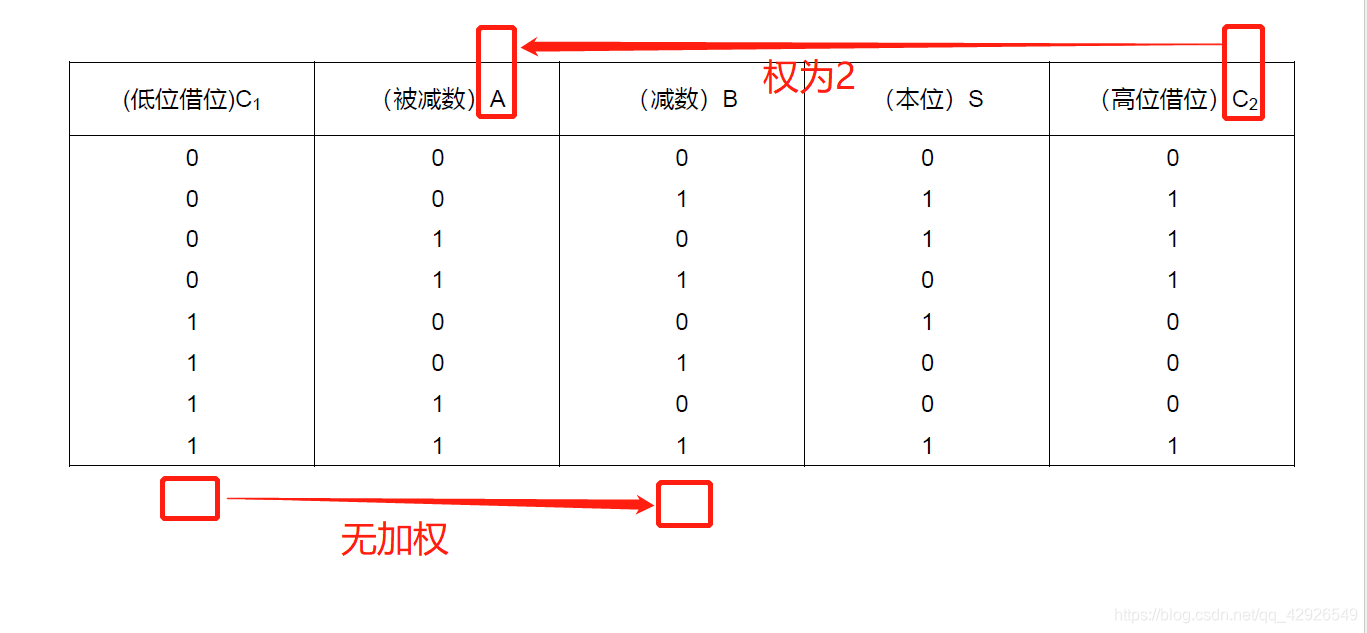

半加器 全加器 全减器的理解 知识的搬运工的博客 程序员宅基地 全减器真值表怎么理解 程序员宅基地

74ls13-8译码器的各输入端的连接情况及第六脚()输入信号 a的波形如下 图所示。试画出八个输出引脚的波形。 解:由74ls138的功能表知,当(a 为低电平段)译码器不工作,8个输出引脚全为高 为高电平段)译码器处于工作 该功能主要用于多显示器 的动态显示。 (3)灯测试功能(lt 此时bi/rbo端作为输出端, 端输入低电平信号时,表1 最后一行,与 及dcba 输入无关,输出 全为"1",显示器7 个字段都点亮。该功能用于7 段显示器测试,判别是否有损坏的字段。

Untitled Document

第8 章combinational Logic Applications Ppt Download

Http My Stust Edu Tw Sys Read Attach Php Id 5849

100學年度第2學期邏輯設計實習ta訓練基本介紹 Ppt Download

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Untitled Document

Untitled Document

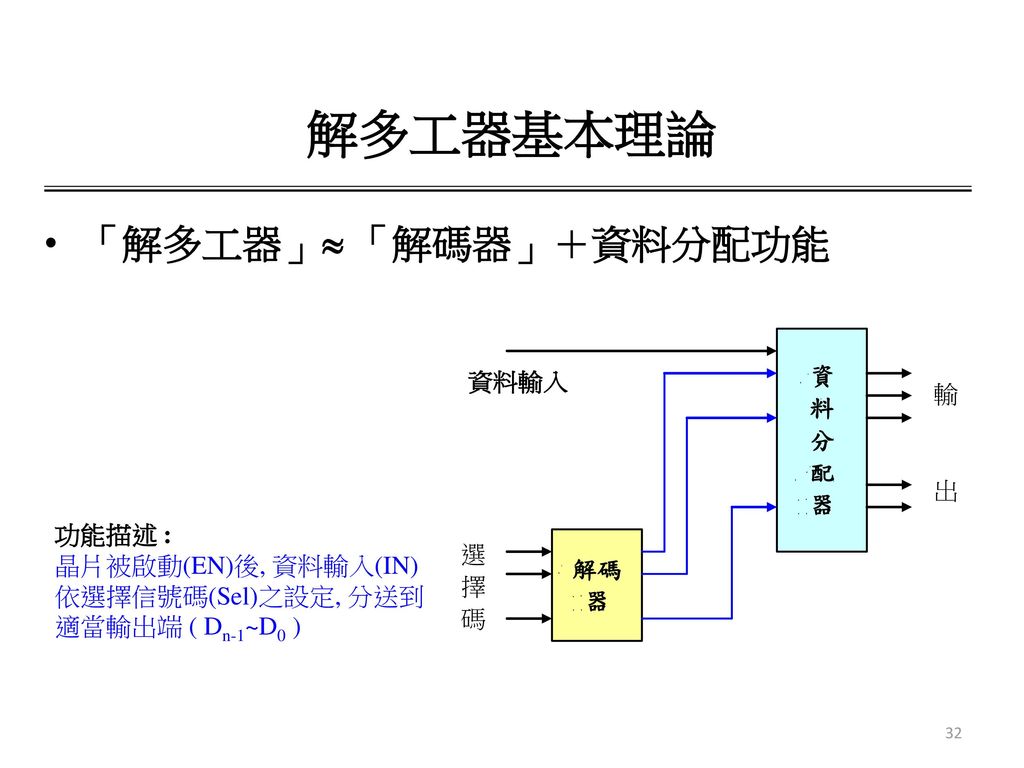

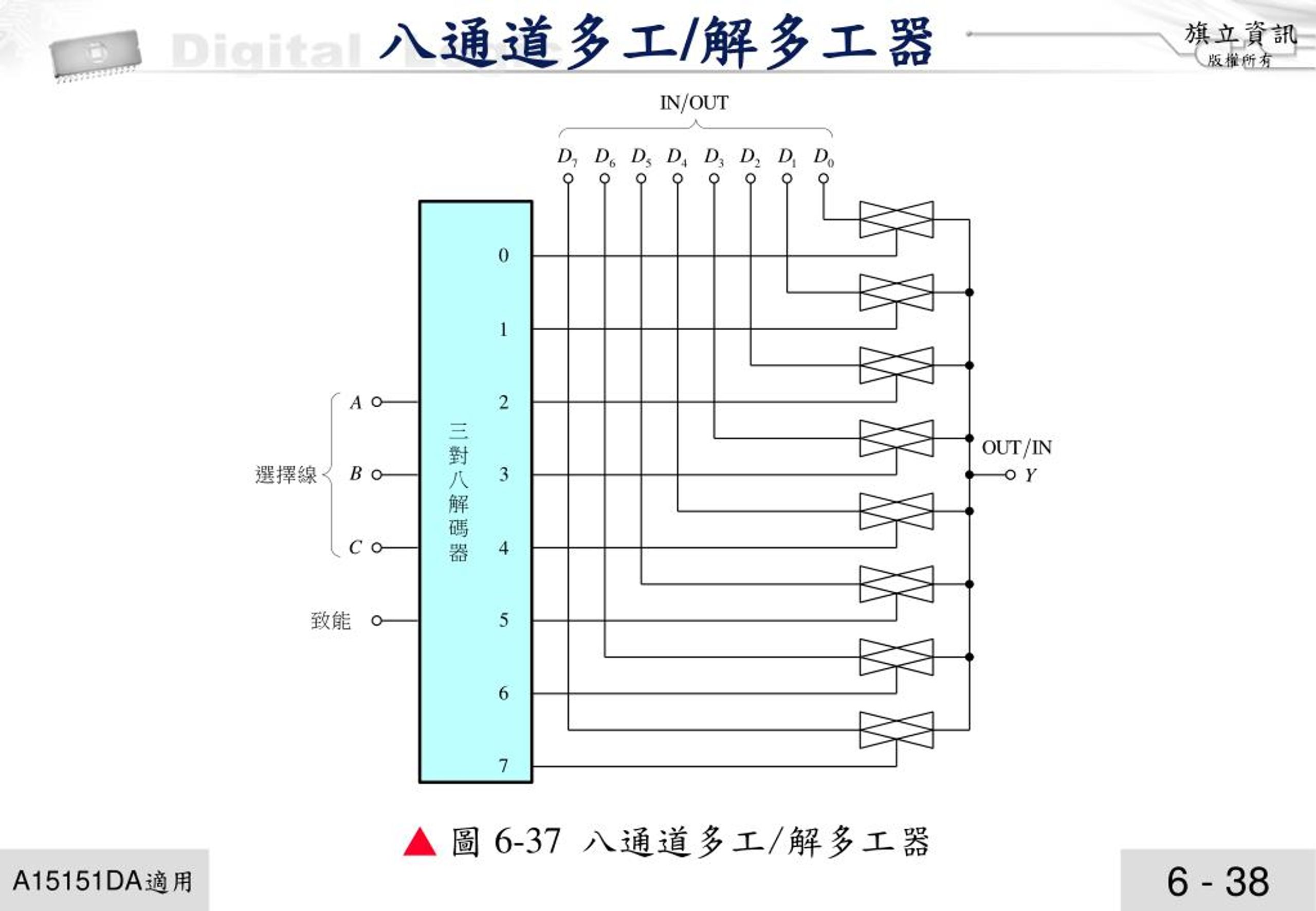

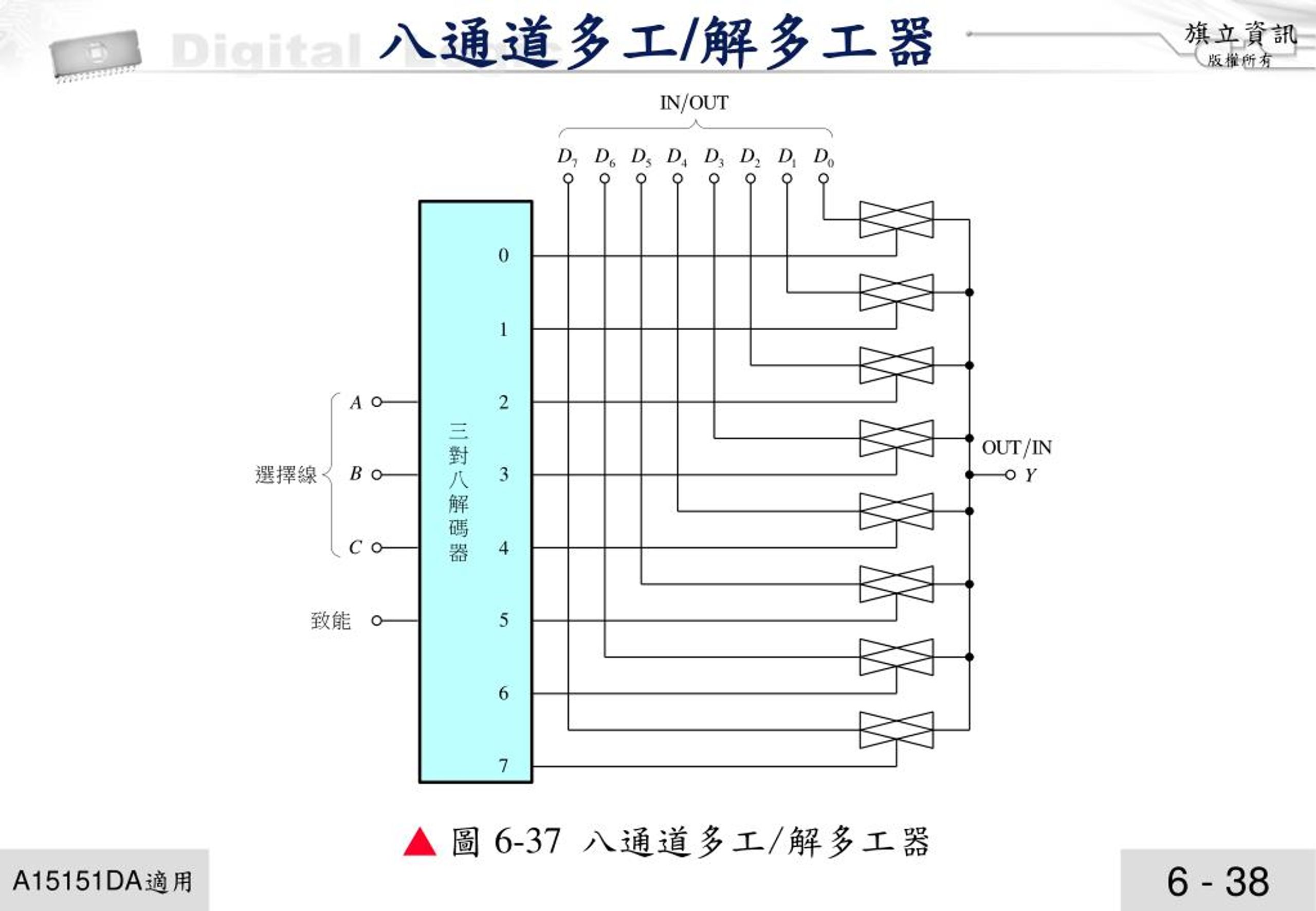

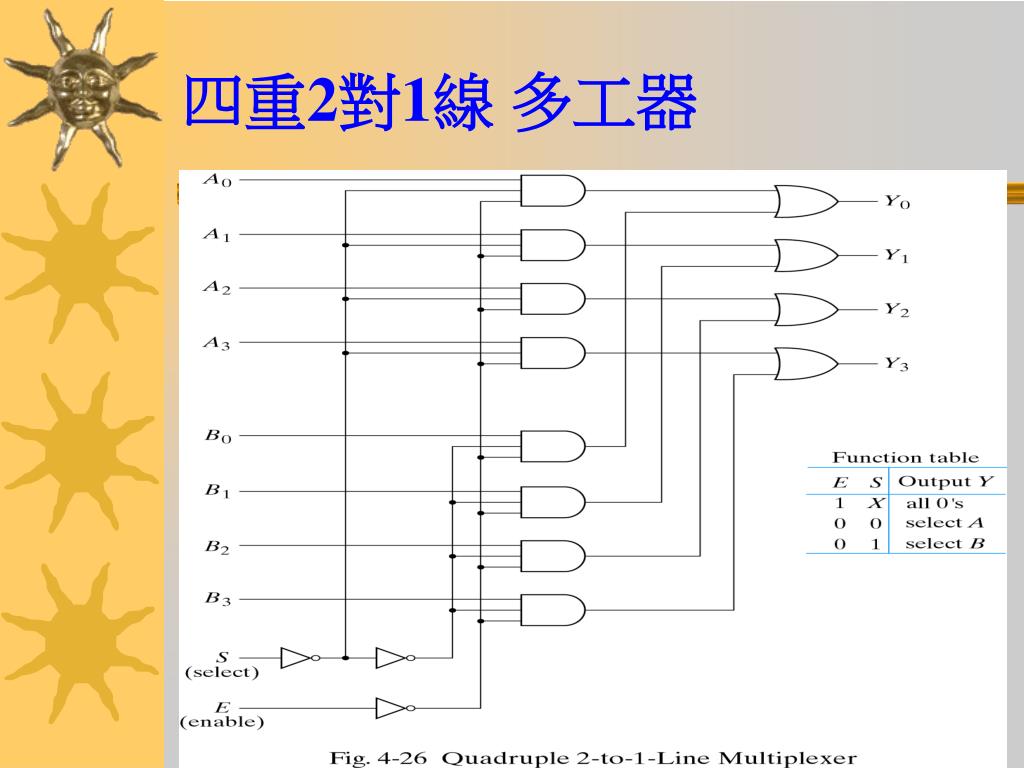

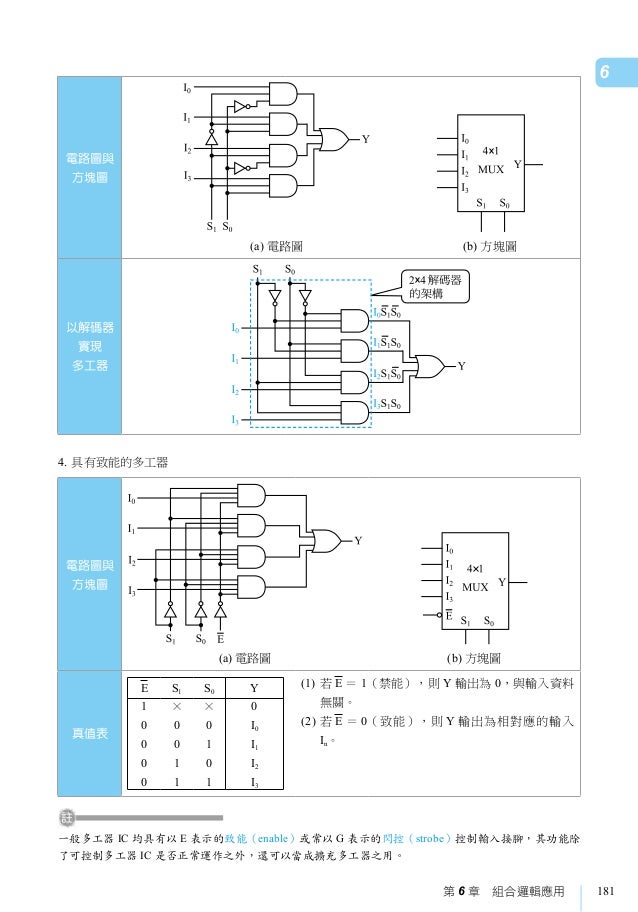

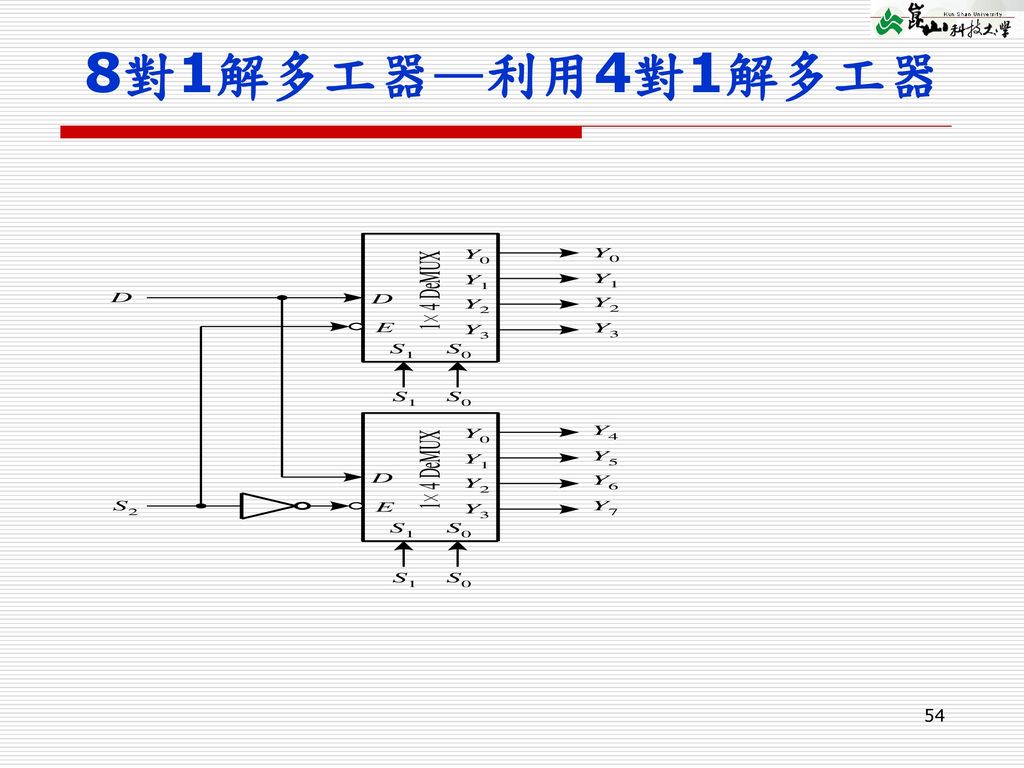

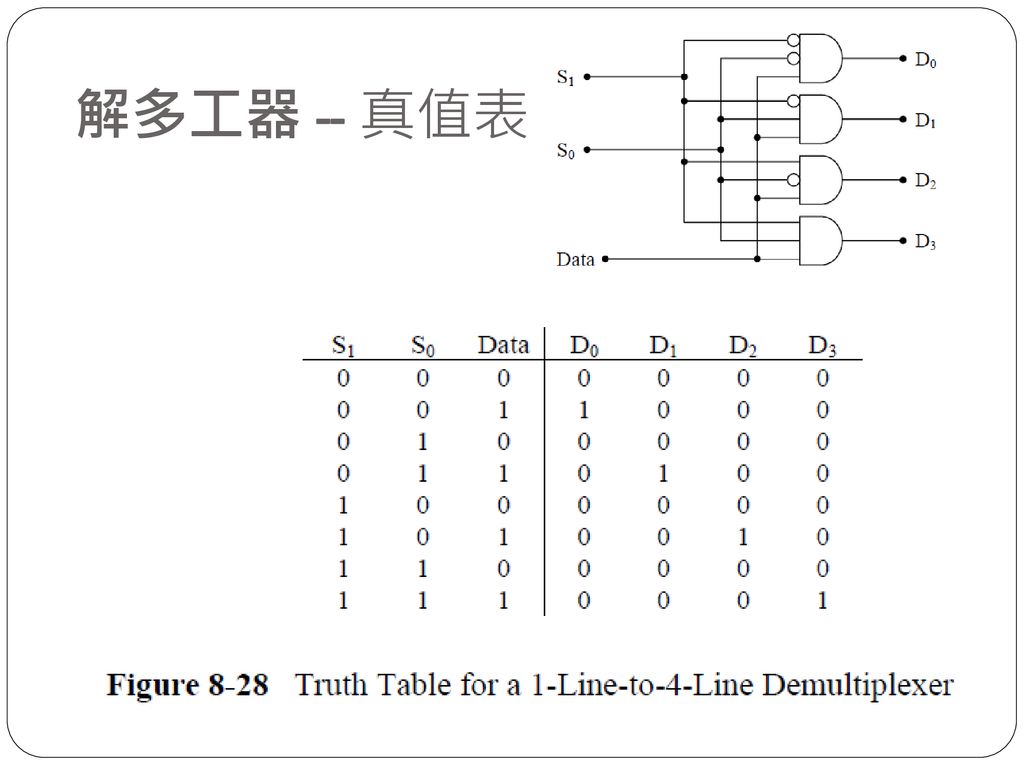

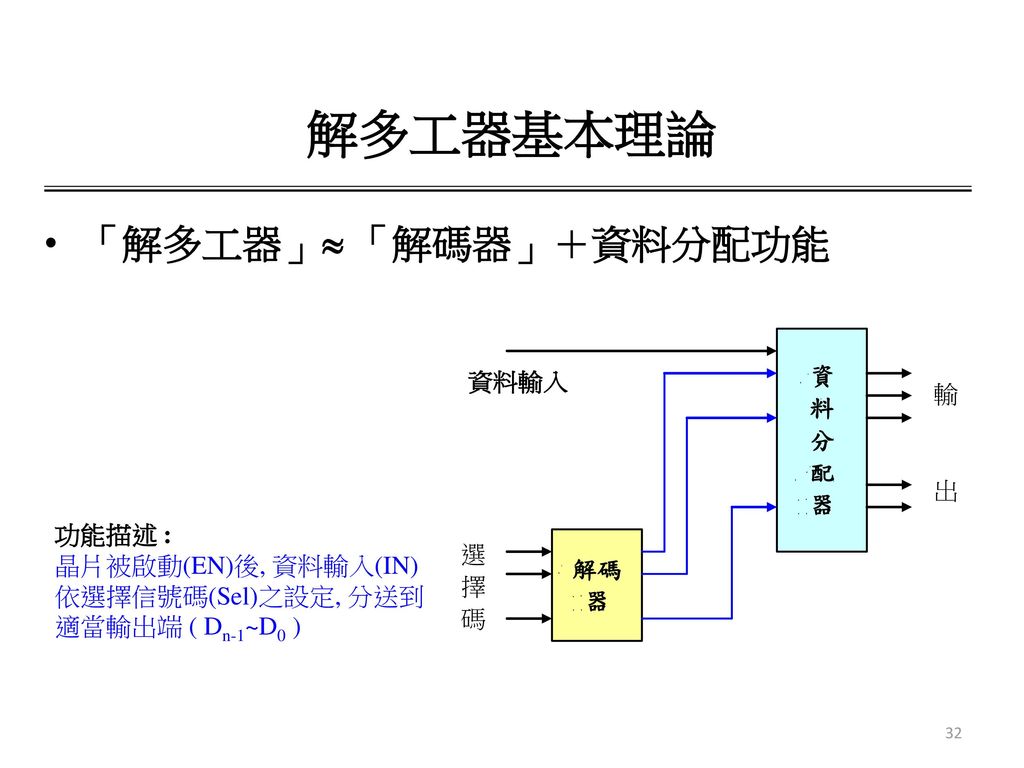

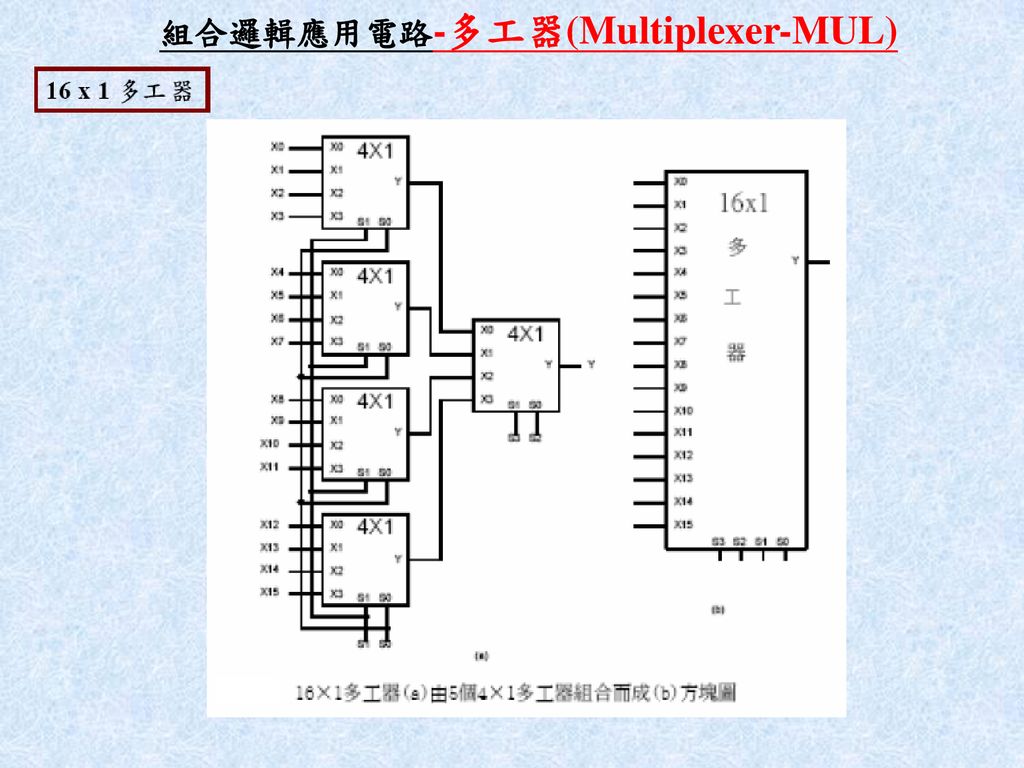

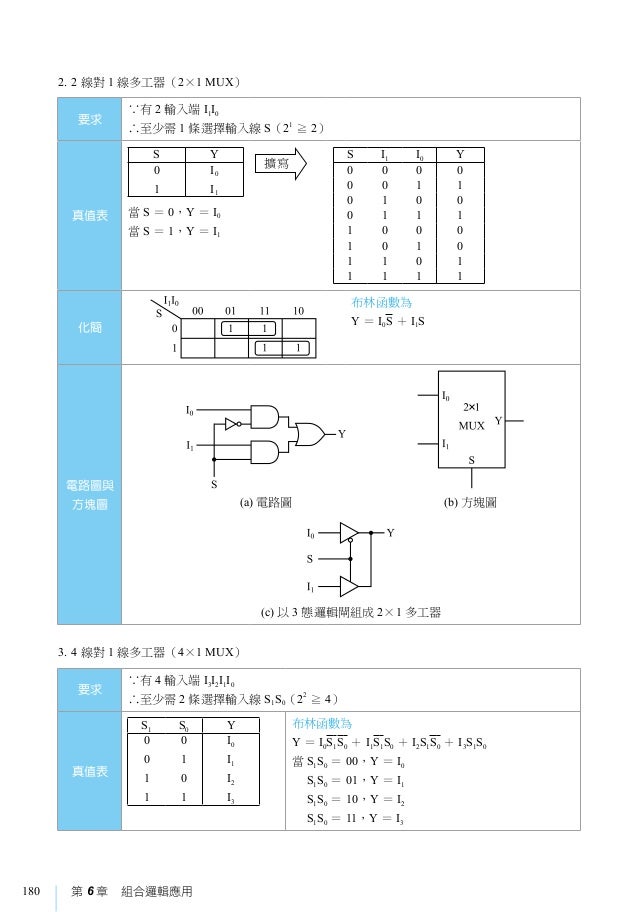

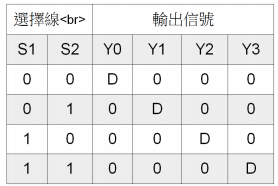

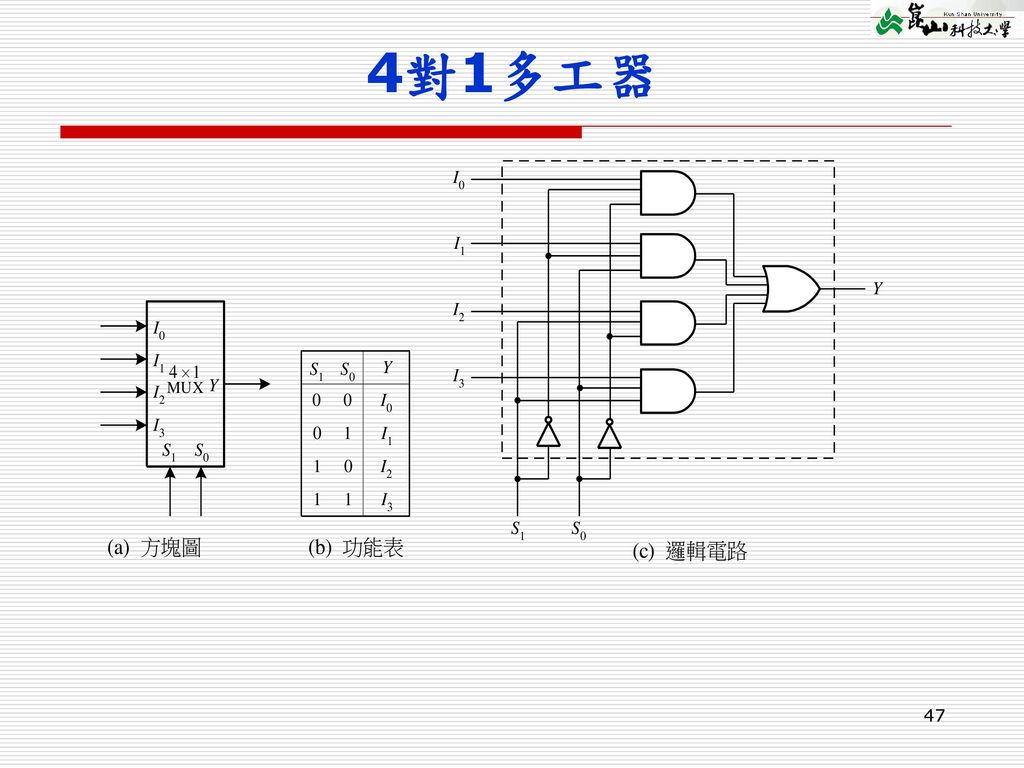

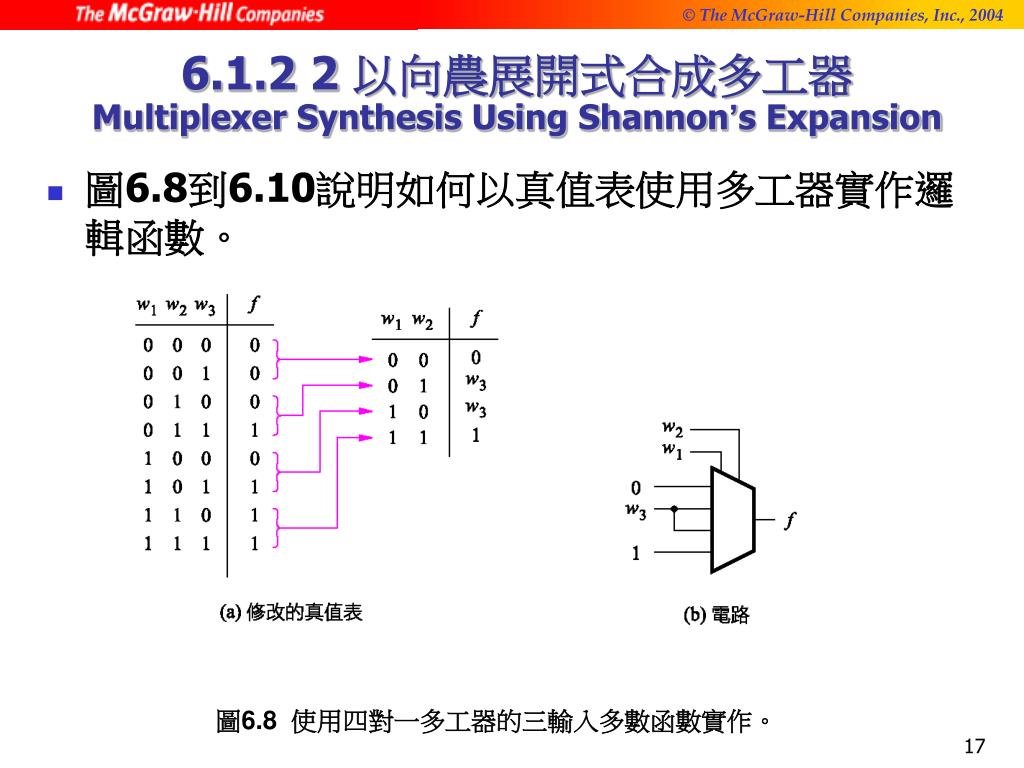

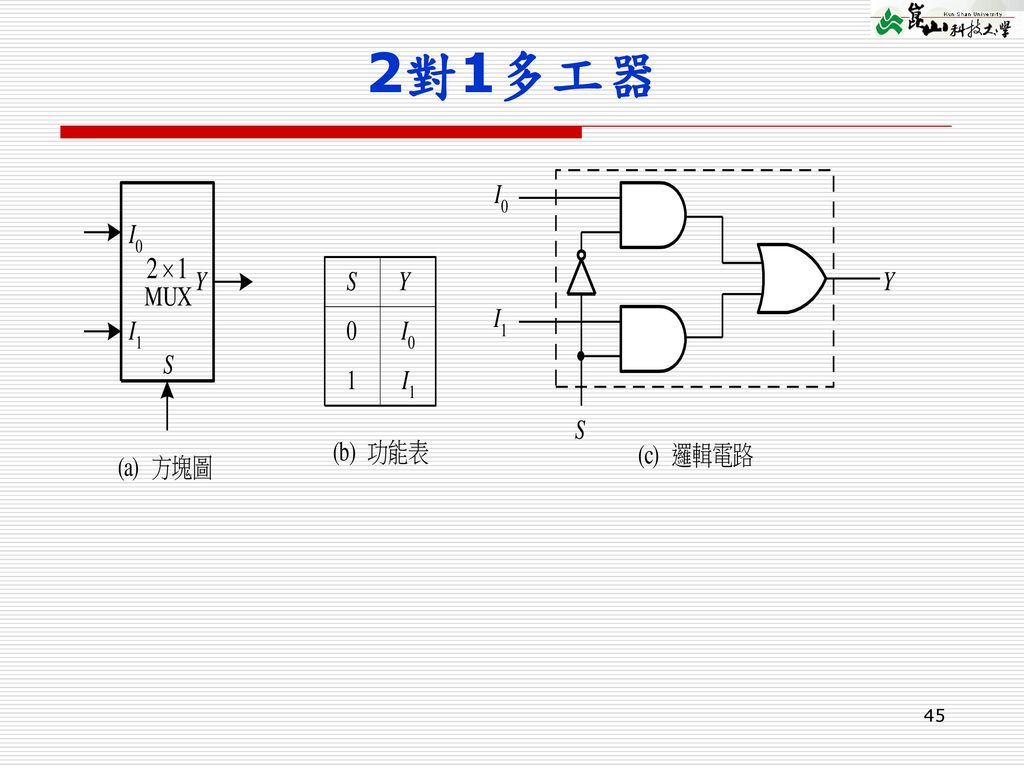

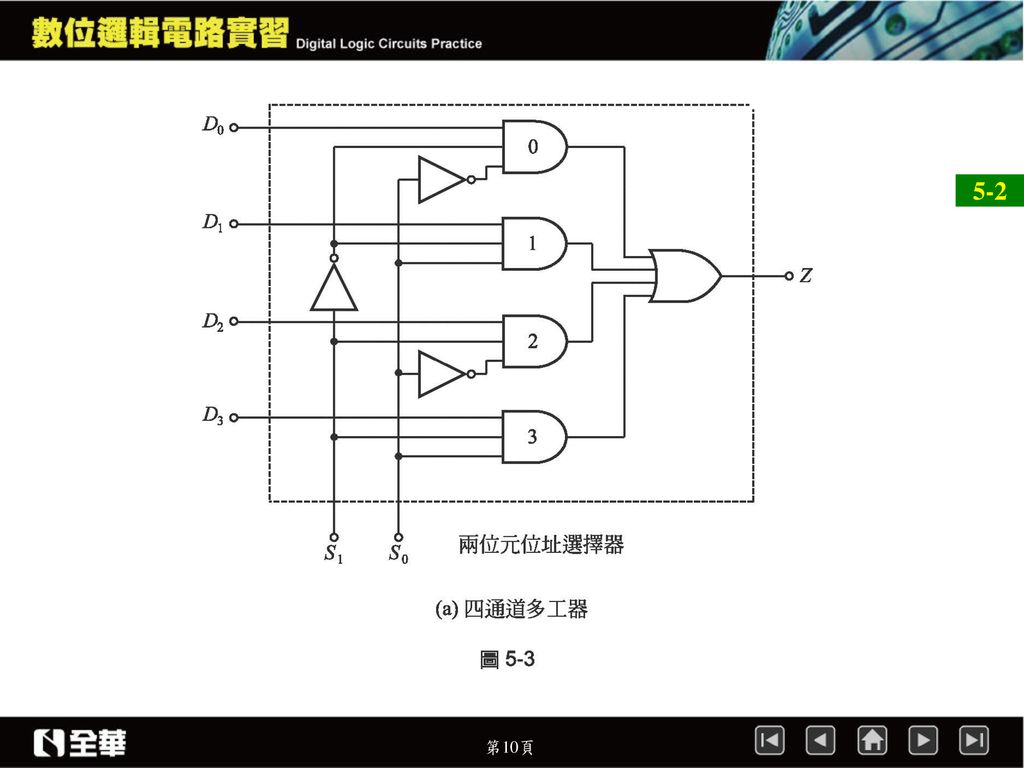

二 相關知識多工器 Multiplexer Mux 或稱資料選擇器 Data Selector 它主要的功能是從許多條資料輸入線 選擇其中一條輸入資料送至單一輸出線上 解多工器 Demultiplexer Demux 的動作和 多工器恰好相反 一般而言 多工器與解多工器是用來執行多段選擇開關的功能

Combinational Circuit Ppt Download

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

Http Eportfolio Lib Ksu Edu Tw User T H 4990k123 Pdf

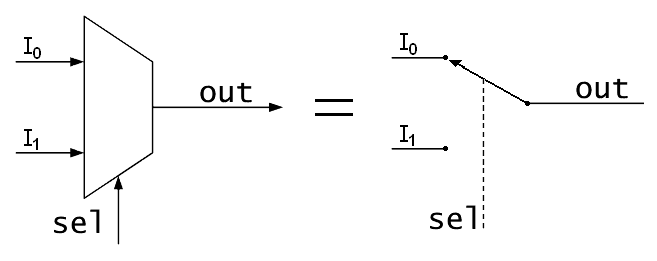

数据选择器 维基百科 自由的百科全书

Www Cyut Edu Tw Yfahuang Chap04 Pdf

数据选择器 维基百科 自由的百科全书

Http Web Nihs Tp Edu Tw Ezfiles 1 1001 Img 28 Pdf

數位邏輯學 第八章

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Lms Hust Edu Tw Sys Read Attach Php Id

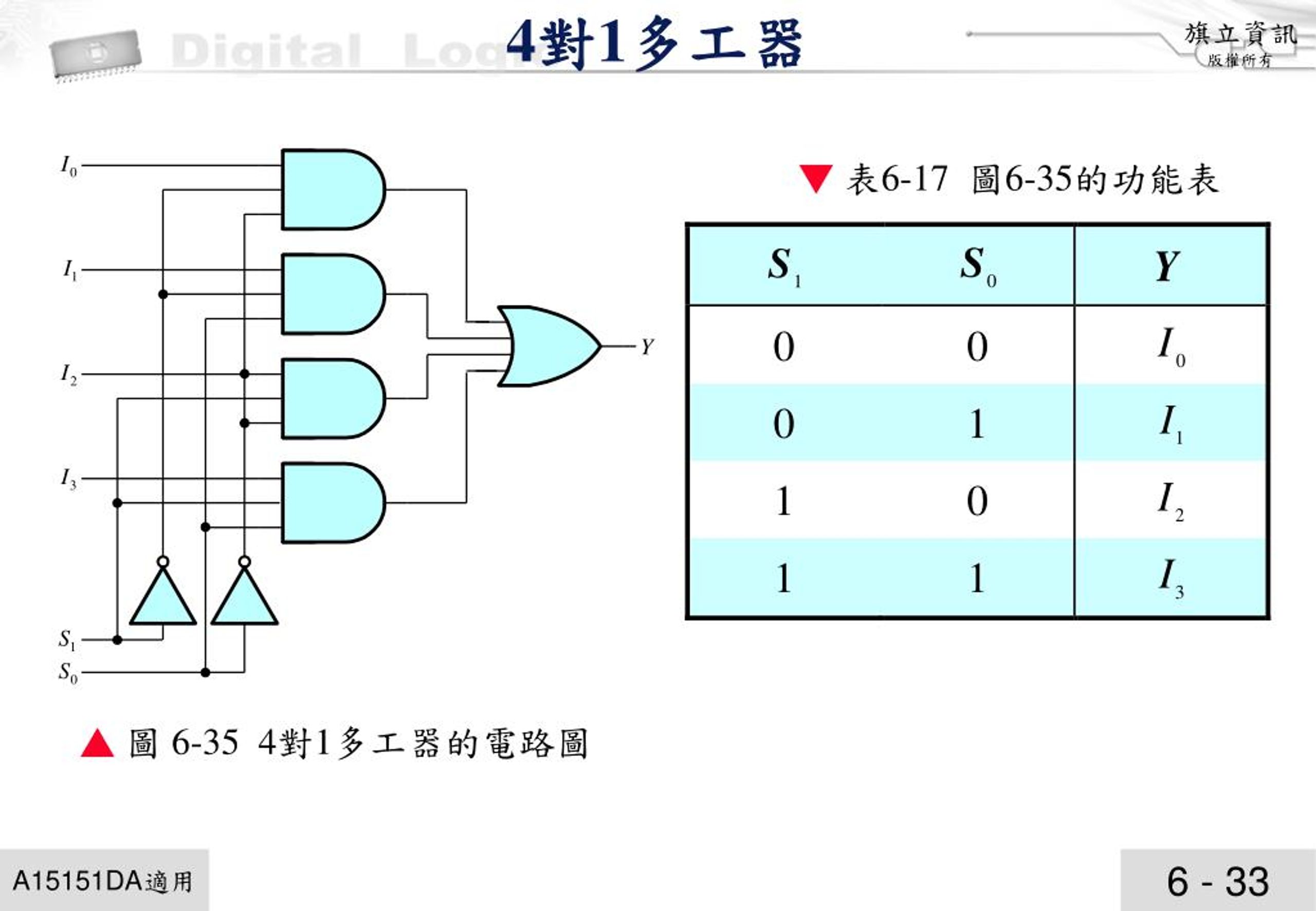

史丹利部落格 多工器4對1

史丹利部落格 多工器4對1

解碼器 維基百科 自由的百科全書

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

數位邏輯學 第八章

掌握 數位邏輯 含實習 複習講義電子試閱本

半加器 全加器 全减器的理解 知识的搬运工的博客 程序员宅基地 全减器真值表怎么理解 程序员宅基地

Cd74hc4067 16 對1 或1 對16 通道 類比 數位 多工器 解多工器 模組 露天拍賣

數位邏輯學 第八章

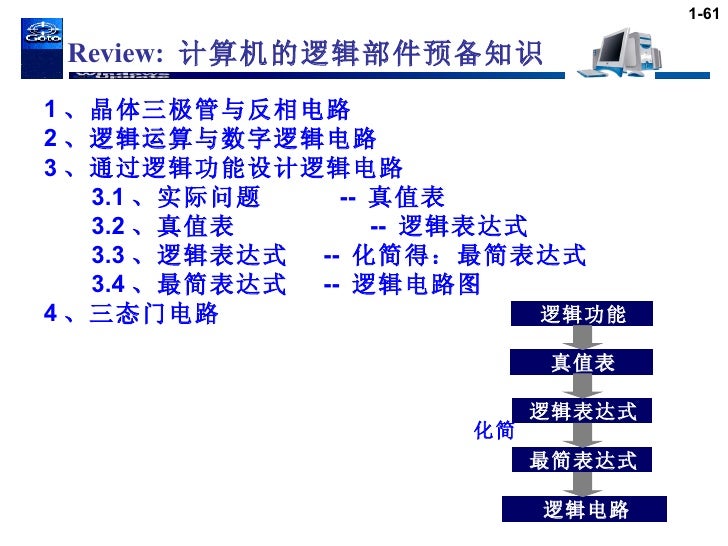

03 计算机的逻辑部件02

Untitled Document

數位邏輯學 第八章

Untitled Document

數位邏輯學 第八章

數位邏輯學 第八章

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Cd74hc4067 16 對1 或1 對16 通道 類比 數位 多工器 解多工器 模組 露天拍賣

數位邏輯學 第八章

Www Cyut Edu Tw Yfahuang Chap04 Pdf

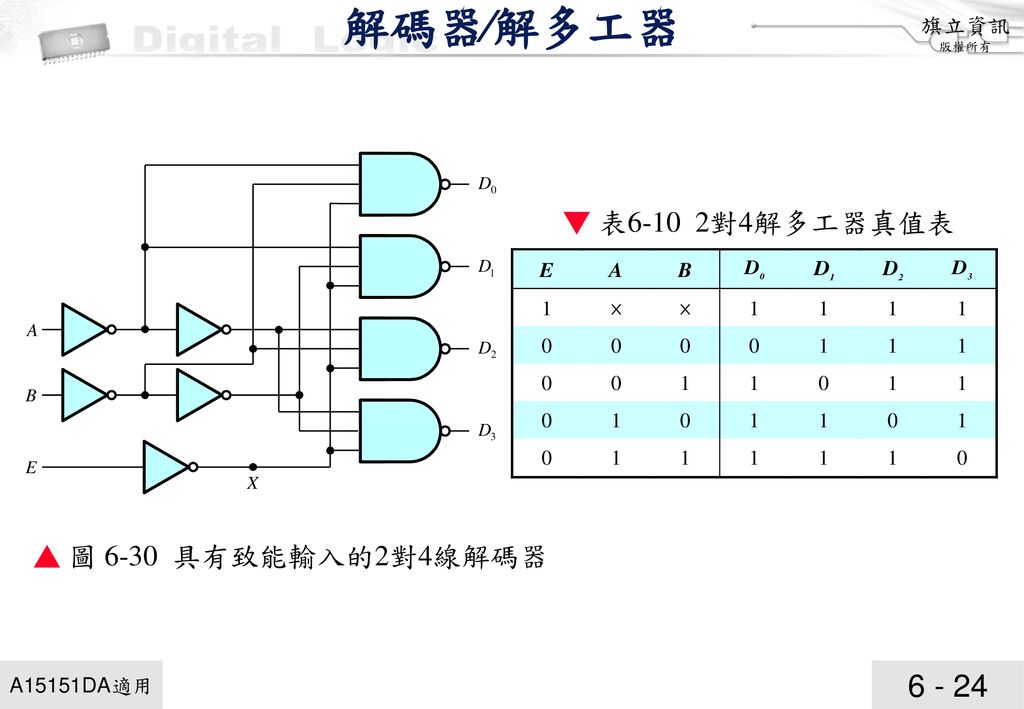

如下為1 對4 解多工器真值表 下列輸出信號之布林函數何者正確 A 阿摩線上測驗

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

Cd74hc4067 16 對1 或1 對16 通道 類比 數位 多工器 解多工器 模組 露天拍賣

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Ppt 第四章powerpoint Presentation Free Download Id

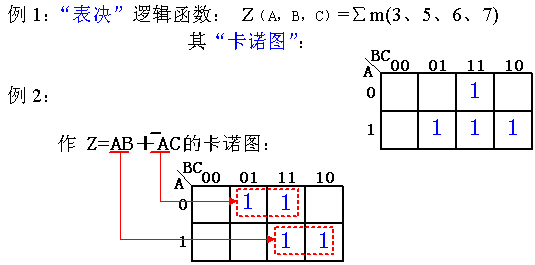

卡诺图 维基百科 自由的百科全书

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

Untitled Document

卡诺图 维基百科 自由的百科全书

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

數位邏輯學 第八章

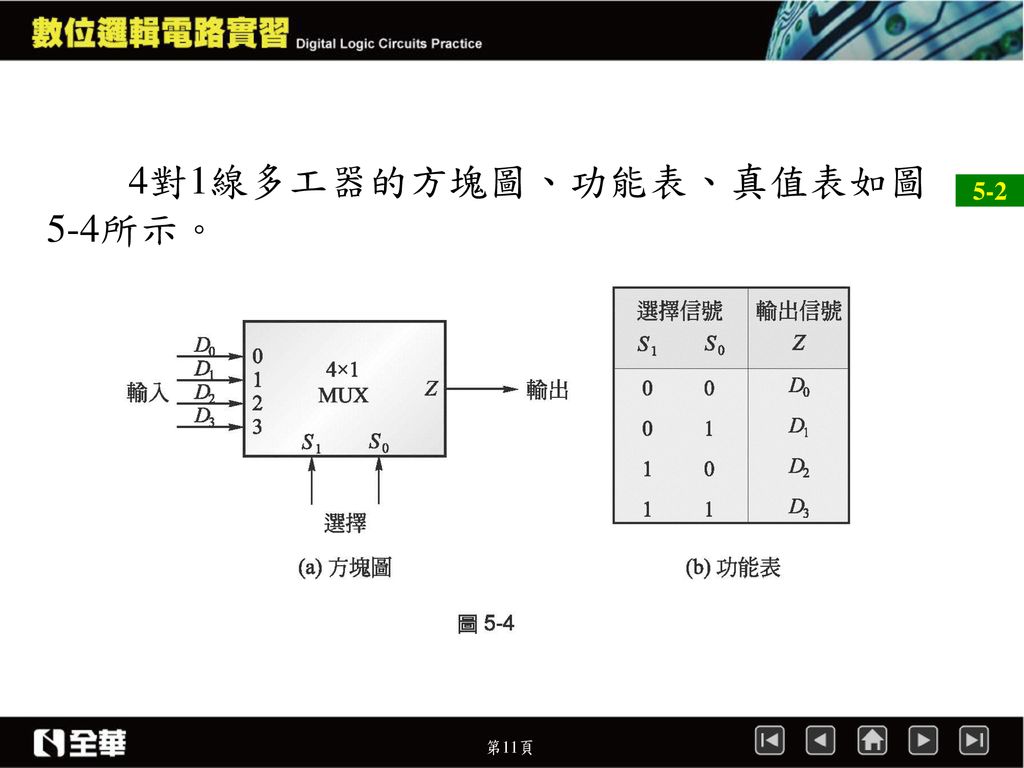

數位邏輯ch6一4x1多工器 Youtube

Untitled Document

Http Job Wnvs Cyc Edu Tw Z361 Attachments Category 14 E6 95 B8 E4 8d E9 8f E8 Afii Pdf

Alex9ufo 聰明人求知心切 Quartus Ii 9 1和de2基本使用方法 入門 2 多工器的設計與模擬

數位邏輯學 第八章

74ls153管脚及功能表 真值表逻辑图及应用电路 电子发烧友网

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

Untitled Document

数据选择器 维基百科 自由的百科全书

Vhdl範例真值表library Ieee Use Ieee Std Logic 1164 All Entity True Is Ppt Video Online Download

Untitled Document

Ppt 數位邏輯powerpoint Presentation Free Download Id

数据选择器74ls153应用电路图大全 表决电路 交通灯 报警电路 电子发烧友网

Untitled Document

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

數位邏輯學 第八章

组合逻辑电路的设计 电子工程世界

74ls153管脚及功能表 真值表逻辑图及应用电路 电子发烧友网

半加器 全加器 全减器的理解 知识的搬运工的博客 程序员宅基地 全减器真值表怎么理解 程序员宅基地

Lms Hust Edu Tw Sys Read Attach Php Id

Ppt 第四章資料處理電路powerpoint Presentation Free Download Id

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

掌握 數位邏輯 含實習 複習講義電子試閱本

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

二 相關知識多工器 Multiplexer Mux 或稱資料選擇器 Data Selector 它主要的功能是從許多條資料輸入線 選擇其中一條輸入資料送至單一輸出線上 解多工器 Demultiplexer Demux 的動作和 多工器恰好相反 一般而言 多工器與解多工器是用來執行多段選擇開關的功能

Http Eportfolio Lib Ksu Edu Tw User T H 4990k075 Pdf

Http Web Nihs Tp Edu Tw Ezfiles 1 1001 Img 28 Pdf

Untitled Document

Http W3 Khvs Tc Edu Tw Ischool Public Resource View Openfid Php Id 2256

掌握 數位邏輯 含實習 複習講義電子試閱本

コメント

コメントを投稿